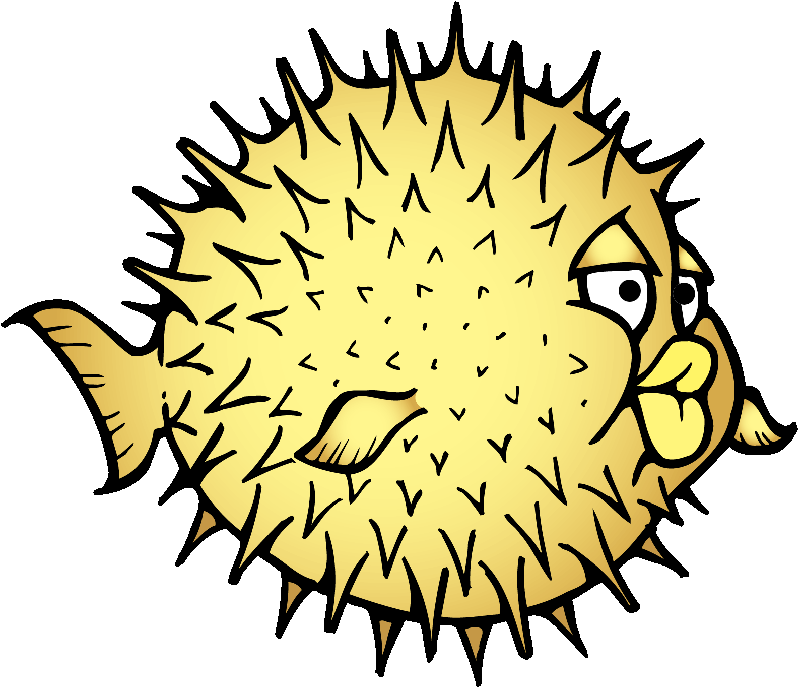

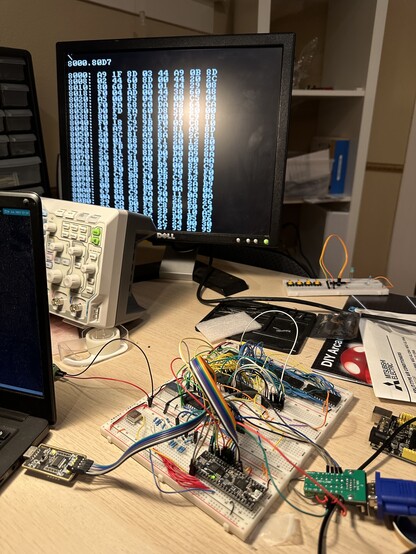

#ZeptoForth boots on the #PicoIce, which means that the default power, usb and flash pins are correctly connected. Which means that #MicroPython and #Mecrisp probably boot as well.

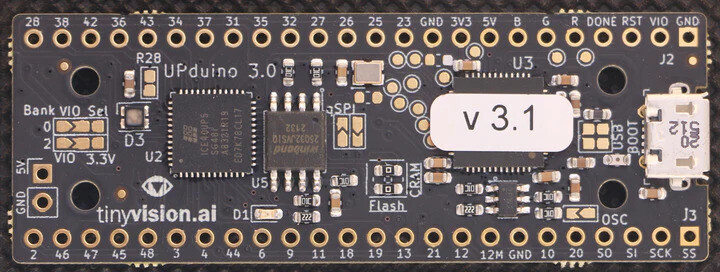

As soon as I get my #FPGA working on the #Upduino, I want to buy a Pico-Ice, and check out the REPLs..