You can find the source code on GitHub (I'm considering moving to Codeberg): https://github.com/projf/isle

Includes everything you need for:

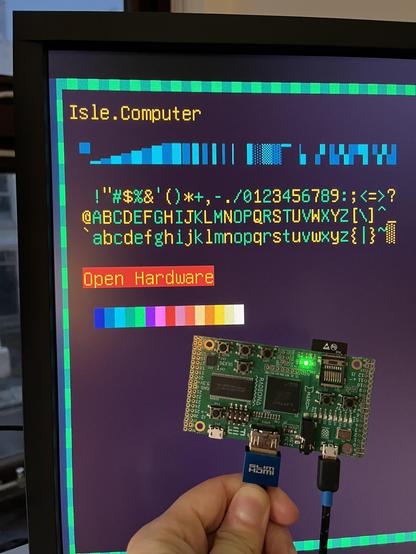

* @machdyne Lakritz (Lattice ECP5)

* Digilent Nexys Video (Xilinx XC7)

* Radiona #ULX3S (Lattice ECP5)

* Verilator simulator with SDL (Linux/macOS/Windows)