This has just the Inmos C011, 5MHz oscillator, decoding logic (CPLD/74*245) and of course some LEDs.

I've added more this time which I hope will give me of an idea when something is working or not.

I've also brought in all 20 bits of the ISA address bus to the CPLD (not that I think I'll need it but just in case).

I've also used DIP chips in case I need change the speed.

Just to be clear:

The #tiny486 is intended as a #devkit for #i486 (in theory even #i386, #i8086 or any other platform that does #ISA (& #PCI) or where one's willing to accept less functionality of a #PC104 compared to #PC104Plus.

As a #BareMetal reference platform for #OS1337 / @OS1337 because there is a demand for a "#BridgeMachine" with new parts even if it's just to do #Archival and #DataRecovery duties and help setup modern drop-in replacements.

- I'd not be surprised if @TechTangents got contacted by some agencies that still have to deal with 8" FDDs and has to basically deny it.

Kevin Karhan :verified: (@[email protected])

Attached: 2 images I still think that a #tiny486 would be cool... https://github.com/OS-1337/tiny486/blob/main/documentation/internal/tiny486-diagram.pdf #PC104 #PC104Plus #RetroComputing #EmbeddedSystems #IndustrialComputing

I still think that a #tiny486 would be cool...

https://github.com/OS-1337/tiny486/blob/main/documentation/internal/tiny486-diagram.pdf

#PC104 #PC104Plus #RetroComputing #EmbeddedSystems #IndustrialComputing

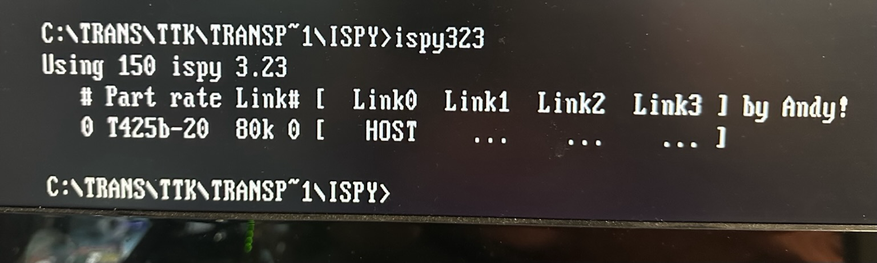

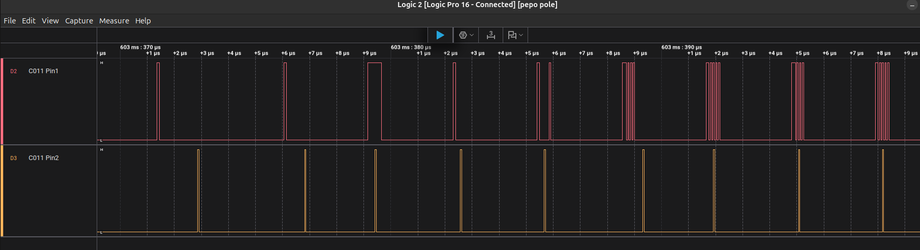

NotLadp and NotSys are two addresses (0x150 and 0x160) and are asserted when the address matches.

PCLK is the ISA bus clock (14.3MHz on my #PC104 PC).

My logic here is that this is a 3 stage ripply counter.

When either address is invalid, the riple counter is reset (.ar = asynchronous reset).

So when an address is valid the IOCHRDY signal will be LOW, i.e. force a wait state.

My #Transputer #pc104 adapter lives!!!

Turns out the CUPL code has two pins inverted (active low) that should not be inverted.

So something isn’t right with the PC timing or the CPLD.

#transputer #pc104

Does anyone have something sub 300Mhz in pc104 they would like to swap?

#PC104 #Transputer woes...

It seems I can write a value to the TRAM (a T425 based one) but when I try to read it back I get rubbish :(

This is my writing 0xAA55AA55 to address 0x8000FF00 (this is a valid address)

but when I read it back, I just get 0x10101010