| Neuromorphic Engineering | https://sites.google.com/d/0B_fY3ol6clHmY1h5OFRxa1NjQmM/p/0B_fY3ol6clHmalpVU1JEcGNFYlU/edit?resourcekey=0-atDquMq9_PQEWqa3EHXeTA |

| Engineering | https://www.youtube.com/channel/UCQxFumV2LMrKBMDW6dar_ZA |

| Discord | iPostHuman#7146 |

iPostHuman

- 25 Followers

- 55 Following

- 1.3K Posts

https://blog.adafruit.com/2025/04/25/pixlens-reality-into-8-bit/

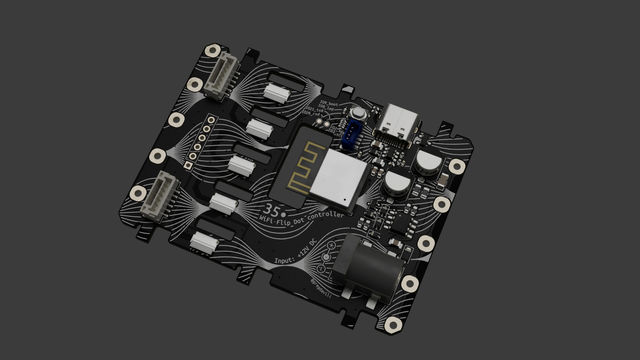

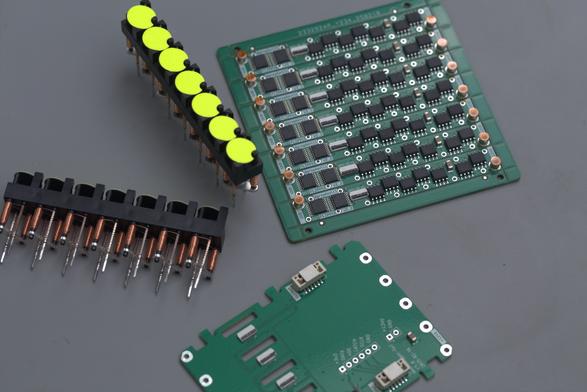

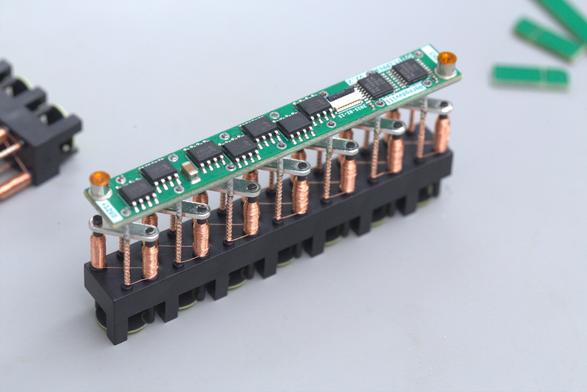

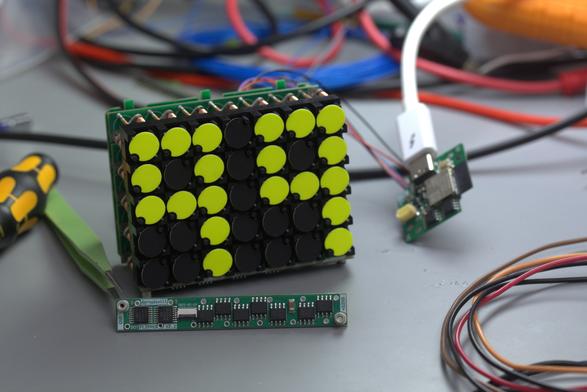

Got a little carried away in inkscape on the silkscreen for this ESP32-C3 based controller board for controlling some flipdot display modules.

Using this plugin from PCM, which makes the KiCad to blender process super easy: https://github.com/30350n/pcb2blender

ASK AN ENGINEER 4/16/2025 LIVE!

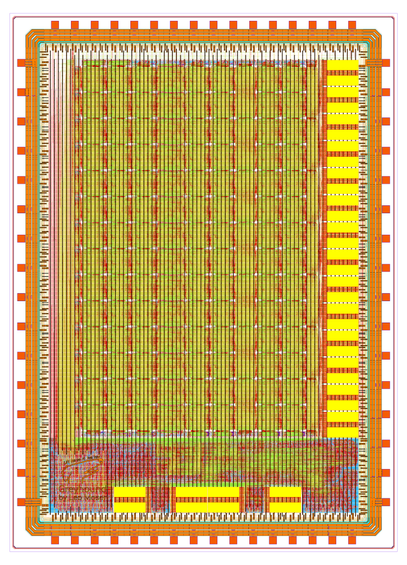

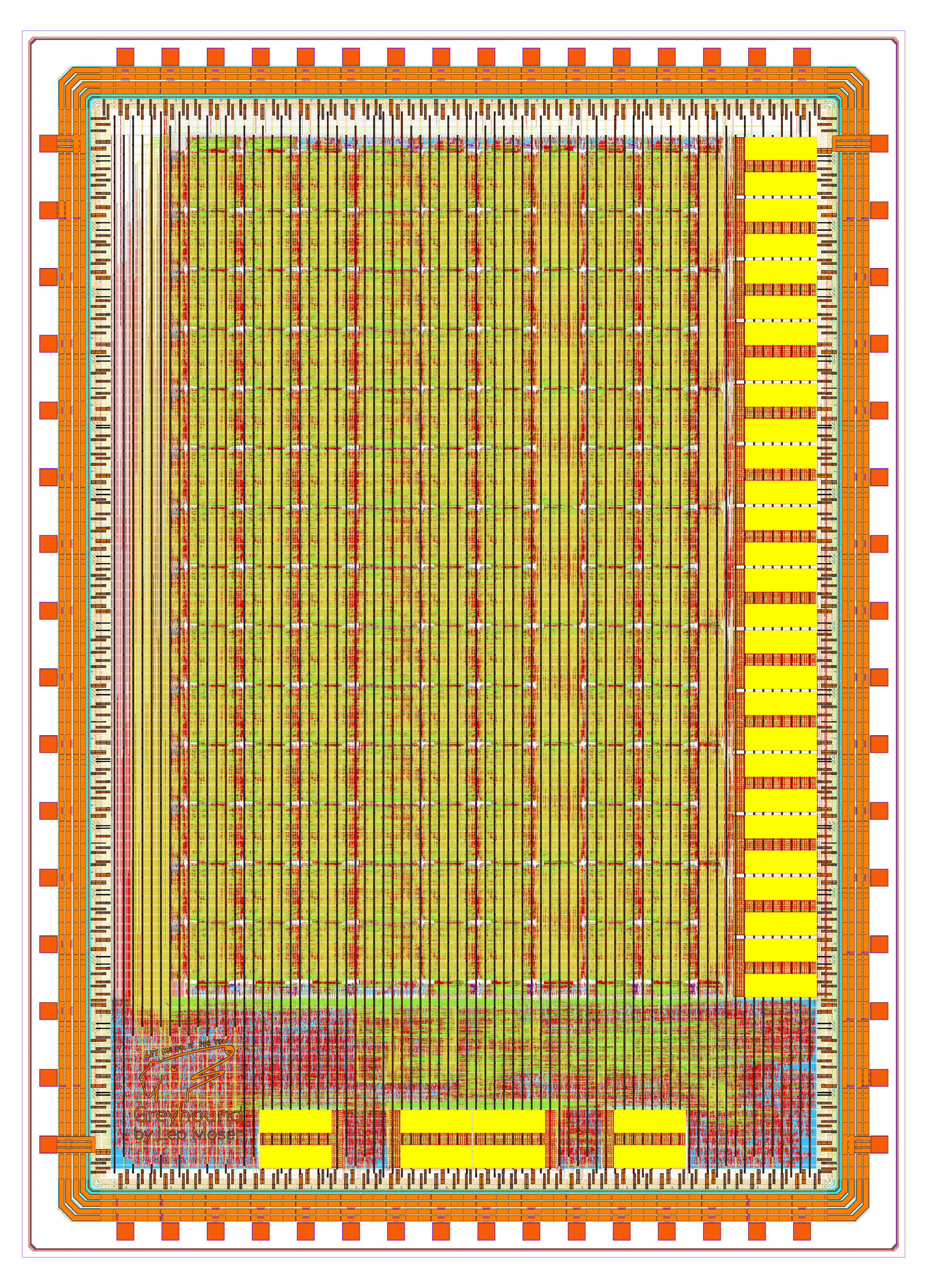

I'm super happy that my latest chip Greyhound has been accepted for production! 🥳

It was designed with open source EDA tools and the IHP Open Source PDK.

Find out more here: https://github.com/mole99/greyhound-ihp

And down below ⬇️

Aerium Lumen – An NVIDIA Jetson carrier board for drones and robots

Aerium System’s Lumen is a carrier board for NVIDIA Jetson SO-DIMM modules designed specifically for drones and robots with a range of low-profile connectors for I/Os for USB, UART, I2C, etc…, and three M.2 sockets for storage and wireless expansion. It targets the same applications as ARK Electronics’ NDAA-compliant Jet…

https://www.cnx-software.com/2025/04/08/aerium-lumen-an-nvidia-jetson-carrier-board-for-drones-and-robots/

TARIFF TALK! WITH LADYADA 🌍🚢 - Join Ladyada as she breaks down how recent tariff shifts impact electronic component availability and pricing, reshoring trends, and what may happen to engineering/BOM and DIY project costs. Get the inside scoop on navigating supply chain challenges while keeping your builds affordable and excellent! All this week on ASK AN ENGINEER WEDS 8PM ET on all the socials.