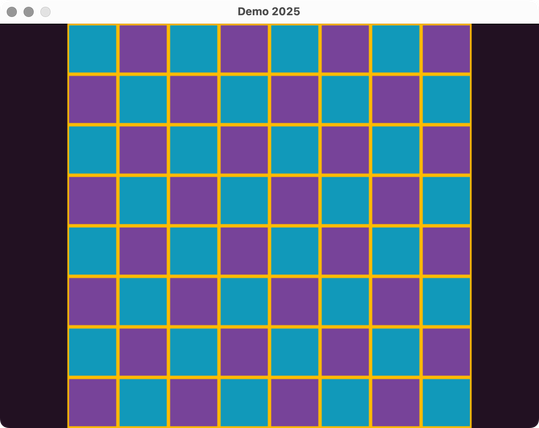

Triangle rasterisation is surprisingly complex. There are multiple approaches and decisions to make on which pixels to include. As part of testing my Earthrise #FPGA graphics engine, I've created visual tests to complement more automated testing.

The #riscv CPU loops over the chessboard, generating the instructions to draw each square, then starts the 2D graphics engine. The CPU can prepare drawings then continue with other things while the graphics engine renders. Here running in Verilator/SDL simulation. #FPGA