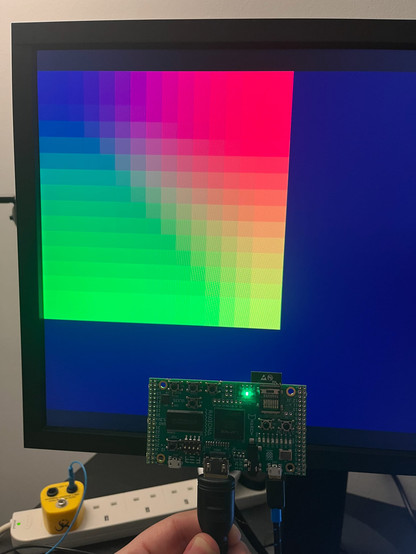

It's #FPGAFriday already! This week, I've got some 1280x720 ULX3S graphics designs for you. Please give them a try and let me know how you get on. This is my first attempt at graphics on ECP5. #FPGA #RadionaOrg

Find the Verilog source & Makefile in git: https://github.com/projf/projf-explore/tree/main/graphics/fpga-graphics